数字锁相环,数字锁相环的分类,数字锁相环参数指标等

1. 触发器型数字锁相环(FF―DPLL)

该环路利用一双稳态触发器作数字鉴相器,其状态分别受输入信号与本地受控时钟信号的正向过零点触发,产生的置位与复位脉冲状态变化之间间隔就反映着两信号之间相位误差。

2. 奈奎斯特型数字锁相环(NR―DPLL)

在输入信号进入数字鉴相器之前,先以奈奎斯特速率(固定速率的时钟脉冲)进行抽样,然后再与本地受控时钟信号进行数字相乘,产生数字式相位误差。 ?

3.过零检测式数字锁相环(ZC-DPLL)

环路用本地受控时钟脉冲对输入信号的过零点抽样,非零的实际抽样值大小就反映着相位误差,用该相位误差来调节本地时钟信号的相位。

4.超前滞后型数字锁相环(LL-DPLL)

这种锁相环的鉴相器将逐周地比较输入信号与本地时钟信号的相位,根据相位的超前或滞后输出相应的超前或滞后脉冲,用变换成加脉冲或减脉冲,对应地调节本地时钟相位。

(1)触发器型鉴相器。下图是该型鉴相器的组成示意图。当检测到输入信号正向过零点时,触发器置“1”,而本地参考信号的正向过零点使触发器置“0”复位。

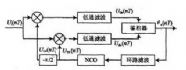

(2) 奈奎斯特速率抽样鉴相器

该型鉴相器组成如下图所示。模数变换器(A/D)的抽样率按带通信号的取样定理选择,以使取样后信号含有充分的输入信号相位信息。